# **Comparative Analysis of Fully** Depleted DMG SOI-MOSFET and SMG **SOI-MOSFET**

### Shikhar Gupta<sup>1</sup>, Prashant Kumar<sup>2</sup>, Anjali Chawla<sup>3</sup>

<sup>1,3</sup>M.TECH Scholar, Dept. of Electronics Engineering, YMCAUST, Faridabad <sup>2</sup>Assistant Professor, Dept. of Electronics Engineering, YMCAUST, Faridabad

Abstract-As the technology is improving there is a need of reducing the short channel effects and body effect. To reduce the body effect, the SOI-MOSFET is used instead of conventional MOSFET. A dual material MOSFET further improve critical parameters to the extent that these devices can be incorporated in integrated circuits at present. In this paper a dual material SOI-MOSFET is analyzed and its performance is compared with single material SOI-MOSFET. The threshold voltage and the sub-threshold swing were found to be reduced in the case of DMG SOI-MOSFET. The device is virtually fabricated and analyzed on ATLAS simulator of SILVACO TCAD Tools.

Keywords: Silicon-on-insulator (SOI), single material gate (SMG), dual material gate (DMG), TCAD, **MOSFET.**

#### I. INTRODUCTION:

During the past few years, CMOS technology is improving its design and high speed performance with the use of high quality material and processing technology. In 1965, Gordon Moore proposed a law which described the evolution of the transistor density in integrated circuits. According to this law, the number of transistors per chip would become four times in every three years. So there is need of shrinking of the size of the transistor. The MOSFET dimensions have to shrink according to scaling law. However, with the reduction of the channel length, undesirable short channel effect arises which causes the dependence of device characteristics, such as threshold voltage on channel length. In contrast to the conventional bulk MOSFET devices, the SOI device has better control on its active silicon layer<sup>[1]</sup>; hence charge sharing effect is substantially reduced. The thin film SOI-MOSFETs offer good electrical characteristics over conventional bulk MOS devices.

In fully depleted SOI, the thickness of active silicon layer tsi must be smaller than source/drain junction depth. In SOI devices, the distribution of non-uniform electric field occurred in the channel with the peak near the drain side. Thus, the charge carriers moving with a low velocity near the source<sup>[2]</sup>, gradually accelerate towards the drain which results in the lower mean carriers transport velocity. When the channel length is small, than there is a probability of hot carrier effect due to high electric field peak near the channel SOI-MOSFET. This result in the formation of drain [3]. There are many methods to reduce the SCE, such potential drop inside the channel, which cause in reduction as use of tantalum gate, which adjust the threshold voltage of the SCEs and uniform electric field distribution along without changing the doping densities. Double gate the channel<sup>[6]</sup>.

structure is also used to improve the SCE and the transconductance of the SOI devices <sup>[4]</sup>.

#### Figure1: Moore's Law

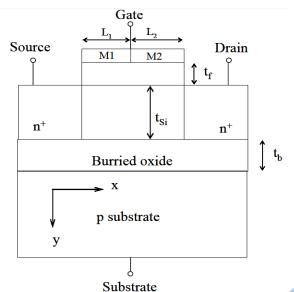

In a Dual Material Gate (DMG) SOI-MOSFET, two different materials with different workfunction are merged together. The workfunction of gate1 (M1) should be greater than the workfunction of gate2 (M2), i.e,  $\phi_{M1} > \phi_{M2}$ <sup>[5]</sup> for n-channel SOI-MOSFET; and  $\phi_{M2} > \phi_{M1}$  for p-

## Shikhar Gupta al. International Journal of Recent Research Aspects ISSN: 2349-7688, Vol. 2, Issue 2, June 2015, pp. 125-128

In this paper, a DMG SOI-MOSFET is designed using Silvaco TCAD Tools. The electrical characteristics of the device; such as threshold voltage, sub-threshold swing is compared with the SMG SOI-MOSFET

#### **II. DEVICE SPECIFICATIONS**

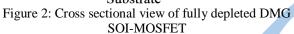

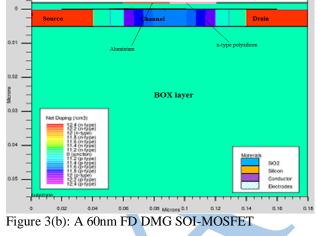

The single material gate SOI MOSFET structure is shown in Fig 3(a) and dual material gate FD SOI MOSFET structure is as shown in Fig. 3(b). The channel length is 60nm; the lengths of source and drain are 60nm. The thickness of oxide layer is 2nm. The thickness of Silicon layer is 5nm. The thickness of buried oxide layer is 50nm. Half of the gate is made up of Aluminium and half of the gate is made up of n-type polysilicon layer. One half of the gate near the source side is made up of Aluminum and the other half of the gate is made up of n-type polysilicon.

Figure 3(a): A 60nm FD SMG SOI-MOSFET

#### **III. DEVICE SIMULATION**

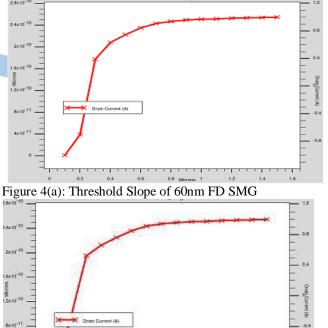

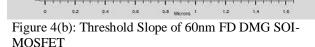

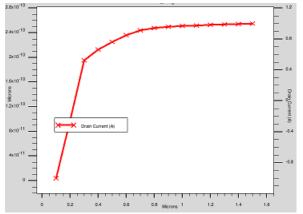

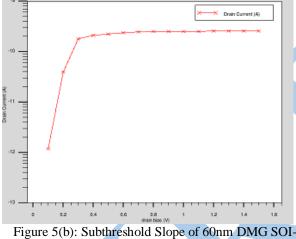

On applying the gate voltage of about 0.4 V and a drain voltage of about 0.1V, the drain current varies almost linearly along the gate voltage. The substrate is kept at zero voltage. The graph shown below shows the variation of drain voltage with respect to the gate voltage. Here, the gate voltage is initialized with a voltage of 0.1V and there is an increment of 0.1V upto 1.5V. The figure 4 shows the threshold voltages curve. The maximum slope of this curve shows the threshold voltage. The figure 5 shows the subthreshold characteristics of the device.

### Shikhar Gupta al. International Journal of Recent Research Aspects ISSN: 2349-7688, Vol. 2, Issue 2, June 2015, pp. 125-128

Figure 5(a): Subthreshold slope of 60nm FD SMG-SOI MOSFET

igure 5(b): Subthreshold Slope of 60nm DMG SOI-MOSFET.

**IV. RESULT**

| Parameter           | SMG                   | DMG                   |

|---------------------|-----------------------|-----------------------|

| Threshold Voltage   | 0.122008 V            | 0.0494949 V           |

| Sub-threshold Swing | 0.0660585<br>V/decade | 0.0710692<br>V/decade |

| Drain current       | 1.24579e-13 A         | 1.60322e-09 A         |

| DIBL                | 0.004416 V/V          | 0.00126166<br>V/V     |

| Ion/Ioff            | 2045.58 A/A           | 785.57 A/A            |

The above table shows the comparisons of the various parameters for fully depleted SMG and DMG SOI-

MOSFET. It is clear that the parameters are improving by using the dual material gate instead of using single material gate.

#### V. CONCLUSIONS

An dual material and single material SOI device on 60nm is designed and simulated on Silvaco TCAD, critical parameters were extracted for analysis. The threshold voltage improvement was observed in the dual materials SOI device, other than this DIBL, Drain current and I<sub>ON</sub>/I<sub>OFF</sub> was also found in DM-SOI devices. The subthreshold swing was observed to be increased with DMG-SOI devices, all these improvements in these critical parameters can be attributed to dual material which is applied in the gate while fabrication. Hence using a DMG-SOI will result in the improvement in the parameters with a bit of design complexity for the integrated circuits of the future. The type of poly-silicon material also affects the performance of the device.

#### VI. REFERENCES

- [1] Y. C. Yeo, V. Subramanian, J. Kedzierski, P. Xuan, T.-J. King, J. Bokor, C. Hu, "Design and Fabrication of 50 nm thin-body p-MOSFETs with a SiGe Heterostructure Channel,"IEEE Transactions. Electron Devices, vol. 49, pp. 279-286, February 2002.

- [2] Priyadarshini Jena, Rajesh Ku Mishra, K. Hari Krishna, "A Comparative Study Of SOI MOSFET Modeling Structure And Their Characterization Through Simulation TCAD Tool", International Journal of Engineering Research & Technology Vol. 1 Issue 10, pp. 1-6, December- 2012.

- [3] O. Adam, K. Higashi, and Y. Fukushima, "Analytical threshold voltage model for ultrathin SOI MOSFETs including short-channel and floating body effects," IEEE Transactions Electron Devices, Vol. 46, pp. 729-737, April 1999.

- [4] S K Mohapatra, K P Pradhan, P K Sahu, G S Pati and M R Kumar, "The effect of interface trapped charges in DMG-S-SOI MOSFET: a perspective study", Advances in Natural Sciences: Nanoscience and Nanotechnology vol. 5, 2014.

- [5] M. Shur, "Split-gate field-effect transistor," Appl. Phys. Letter, vol. 54, no. 2, pp. 162–164, 1989.

- [6] W. Long, H. Ou, J.-M. Kuo, K. K. Chin, "Dual material gate (DMG) Field Effect Transistor," IEEE Transactions Electron Devices, vol. 46, pp. 865-870, May 1999.

- [7] Anurag Chaudhry, M. Jagadesh Kumar, "Controlling Short-channel Effects in Deep Submicron SOI MOSFETs for Improved Reliability: A Review", IEEE Trans. on Device and Materials Reliability, Vol.4, pp.99-109, March 2004.

- [8] K. K. Young, "Short-channel effects in fully depleted SOI MOSFET's," IEEE Transactions Electron Devices, vol. 36, pp. 399-402, 1989.

- [9] Baker, R. J. "CMOS: Circuit Design, Layout, and Simulation" John Wiley and Sons. 1208 p, 2010.

# Shikhar Gupta al. International Journal of Recent Research Aspects ISSN: 2349-7688, Vol. 2, Issue 2, June 2015, pp. 125-128

- [10] Robert Boylestad, Louis Nashelsky, "Electronic Devices and Circuit Theory", 7e Prentice Hall, pp. 211-242.

- [11] S.M Kang, Yusuf Leblebici, "CMOS Digital Integrated Circuits: Analysis and Design", 3e, McGraw-Hill Higher Education.

- [12] M. Jagadesh Kumar, Anurag Chaudhry, "Two-Dimensional Analytical Modeling of Fully Depleted DMG SOI MOSFET and Evidence for Diminished SCEs," IEEE Transactions on Electron Devices, vol. 51, no. 4, pp. 569-574, April 2004.