# Design and Analysis of Low Power High Gain Operational Amplifier

# <sup>[1]</sup> Dr.S.Syed Ameer Abbas, <sup>[2]</sup> K.Kamaraj, <sup>[3]</sup> S.Elma Rani, <sup>[3]</sup> S.Priyadarsini

<sup>[1]</sup> Professor, Department of ECE, Mepco Schlenk Engineering College, Sivakasi,

<sup>[2]</sup> Assistant Professor, Department of ECE, Mepco Schlenk Engineering College, Sivakasi,

<sup>[3]</sup> PG Scholar, Department of ECE, Mepco Schlenk Engineering College, Sivakasi,

Abstract— Operational amplifiers are used to achieve low power and high gain. Because low power and high gain are the major requirements for monitoring and recording bio-potential signals. In this paper a two-stage amplifier is designed, with the first stage being a simple differential stage and the second stage is a common source stage, having a compensation capacitor. In between the first and the second stage a current mirror topology is used that works as a sink for the current. The current mirror sums the differential current of first stage, feeding it to the second stage by the current mirror action. The proposed Op-Amp operates at 1V supply voltage and consumes a total power of  $4\mu$ W with the gain  $\geq 98dB$ . The proposed design has been implemented using Advanced Design System (ADS) for 80nm CMOS technology.

Index Terms— Operational amplifier, High gain, Low power, ADS.

# I. INTRODUCTION

Rapid developments in medical science have led to the daily use of biomedical equipment. The functions of biomedical equipment have become increasingly complex along with the inbuilt electronic circuitry. It has become a trend to miniaturize and integrate the electronic circuits in biomedical systems. Main purpose of the implantable integrated circuits is to measure the neural signals like AP's (Action potentials) and LFP's (Local field potentials) helps many neurological analysis and Neuroprosthetics. Reading accurate results of this neural potentials helps to diagnose many neural disorders like Parkinson's disease and ALS (Amyotrophic Lateral Sclerosis) [2].

Operational amplifiers (Op-Amps) are an integral part of many analog and mixed signal systems. As the demand for mixed mode increased, the development of electronics, information technology (IT) and communications has been mainly enabled by nonstop development in silicon based complementary metal oxide semiconductor technology. Operational amplifier has direct coupling, high gain and low power. It is a versatile device that can be used to amplify ac as well as dc input signals.

In analog circuits, settling behavior of the Op-Amp determines the accuracy and speed of the circuit. High accuracy and fast settling requires a high DC gain and a high Unity gain frequency respectively. Cascading multiple stages and enhancing output impedance are two of the common methods to increase the DC gain. Cascading two or more stages can produce high DC gain yet applicable for lowvoltage applications. However cascading results in stability issues. Thus much more design efforts are required in order to compensate these issues [3].

Output impedance enhancement can be implemented using different methods, e.g. cascading, gain boosting and applying positive feedback. Employing the cascade configuration and gain boosting requires at least stacking four transistors from top rail to bottom rail. This consumes more voltage head, which may not be appropriately implemented in low-voltage circuits. Therefore the proposed method overcome this issues because low power and high gain are required to monitor and record bio-potential signals for medical diagnosis. The coupling of bio-potential signals from the body into the electronic equipment is accomplished through electrodes. These electrodes interface ionic currents in the body with electrical currents in the electronic instruments [7].

# II. PROPOSED METHODOLOGY

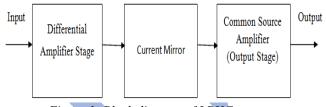

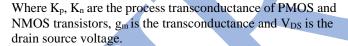

A two-stage amplifier is designed, with the first stage being a simple differential stage and the second stage is a common source stage, having a compensation capacitor. In between the first and the second stage a current mirror is used that works as a sink for the current. The current mirror sums the differential current of first stage, feeding it to the second stage by the current mirror action as shown in Figure 1. This topology provides highly stable system with a high gain and it also provides low power dissipation.

Figure 1: Block diagram of LPHG op-amp

# A. Differential amplifier

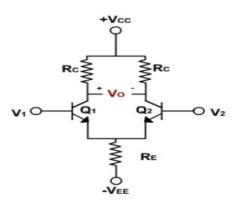

A differential amplifier is a type of electronic amplifier that amplifies the difference between two input voltages. It is an analog circuit with two inputs  $V_1^+$  and  $V_2^-$  and one output  $V_0$  in which the output is ideally proportional to the difference between the two voltages.

$$V_0 = A (V_1^+ - V_2^-)$$

(1)

Where A is the gain of the amplifier

The differential amplifier stage achieves high gain in the system. The inputs are given as out of-phase to the common source NMOS connected in differential form as shown in Figure 2.

Figure 2: Differential amplifier

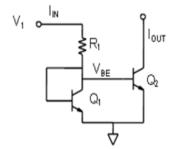

#### **B.** Current mirror

A current mirror is a circuit block which functions to produce a copy of the current flowing into or out of an input terminal by replicating the current in an output terminal. An important feature of the current mirror is a relatively high output resistance which helps to keep the output current constant regardless of load conditions. Another feature of the current mirror is a relatively low input resistance which helps to keep the input current constant regardless of drive conditions. The current being copied is often a varying signal current. The current mirror is often used to provide bias currents and active loads in amplifier stages. I<sub>IN</sub> and I<sub>OUT</sub> are the input and output current as shown in Figure 3.

Figure 3: Current mirror

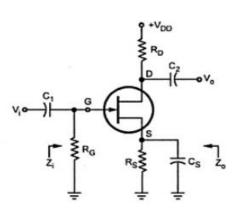

#### C. Common source amplifier

A common source amplifier is one of the three basic single field effect transistor (FET) amplifier topologies, typically

| S.NO. | Transistors                                                      | W(m) &<br>L=80nm |

|-------|------------------------------------------------------------------|------------------|

| 1     | M <sub>1</sub> ,M <sub>2</sub>                                   | 1.8µ             |

| 2     | M <sub>3</sub> ,M <sub>4</sub>                                   | 3.89µ            |

| 3     | M <sub>5</sub> ,M <sub>10</sub> ,M <sub>16</sub>                 | 0.225µ           |

| 4     | M <sub>6</sub> ,M <sub>7</sub> ,M <sub>11</sub> ,M <sub>12</sub> | 1.53µ            |

| 5     | M <sub>8</sub> ,M <sub>9</sub>                                   | 80n              |

| 6     | M <sub>13</sub>                                                  | 9.5µ             |

| 7     | M <sub>14</sub>                                                  | 6.28µ            |

| 8     | M <sub>15</sub>                                                  | 2.7µ             |

used as a voltage or transconductance amplifier.

#### Figure 4: Common source amplifier

Bandwidth of common-source amplifier tends to be low, due to high capacitance resulting from the Miller effect. The gate-drain capacitance as shown in Figure 4 as  $C_1$  and  $C_2$  is effectively multiplied by the factor  $1+|A_v|$ , thus increasing the total input capacitance and lowering the overall bandwidth. The Miller effect is given by

$$C_{\rm M} = C \ (1 + A_{\rm v})$$

(2)

### (3.2)

Where C is the feedback capacitance and  $A_v$  is the gain of the amplifier.

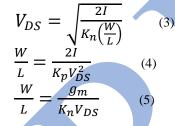

The W/L ratio for the transistors are calculated using

Figure 5: Schematic of low power high gain (LPHG) opamp

The Width (W) of each transistors used in the schematic for 80nm technology are tabulated in Table 1.

Table 1: Design specification of the transistors

Dr.S.Syed Ameer Abbas et al. International Journal of Recent Research Aspects ISSN: 2349-7688, Vol. 4, Issue 4, Dec 2017, pp. 312-315

# **III. RESULTS AND DISCUSSION**

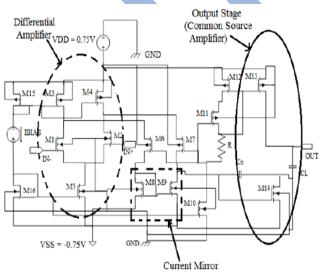

Advanced Design System (ADS) is electronic design automation software. It is used for the performance evaluation of the proposed LPHG Op-Amp at 80nm CMOS technology. Figure 6 shows the schematic representation in ADS which is drawn using the available components. Then perform necessary simulation to calculate gain and power. It has two stages namely differential and common source stage. In between there is a current mirror which adds the current output of differential stage.

Figure 6: Schematic of LPHG op-amp in ADS

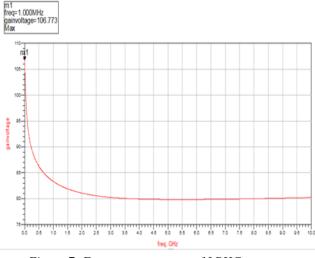

AC analysis is done to calculate the gain. The gain is calculated using Gain = 20 log  $* \frac{V_o}{V_i}$  (dB) where V<sub>o</sub> and V<sub>i</sub> are the output and input voltage of the system.

The high gain enables the proposed circuit to perform efficiently in the closed loop system. Figure 7 shows the obtained gain voltage is 106.733dB at 1MHz.

Figure 7: Frequency response of LPHG op-amp

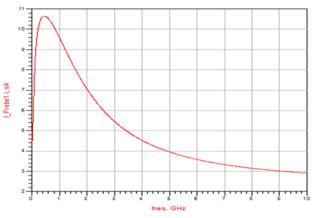

To calculate power dissipation, current value should be known. Therefore a current probe is connected at the output side and the current value is shown in Figure 8.

Figure 8: Current at the output stage

The average power dissipation is calculated as  $4.5\mu W$  using the formula

$P_avg = p_inst (l_Probe1i, nA)$ (7)

The Table 2 shows the performance of proposed method. The gain has increased and the power dissipated is also reduced to  $\mu W$  range.

| Table 2: Performance of the designed LPHG op-amp |                |        |           |

|--------------------------------------------------|----------------|--------|-----------|

| Parameters                                       | Specifications | [1]    | Results   |

|                                                  |                |        | Obtained  |

| Technology                                       | 80nm           | 90nm   | 80nm      |

|                                                  |                |        |           |

| Gain                                             | $\geq$ 98dB    | 93dB   | 106.733dB |

| C 1                                              | 1 7 7          | 0.751  | 177       |

| Supply                                           | 1V             | 0.75V  | -1V       |

| voltage                                          |                |        |           |

| Power                                            | 4µW            | 1.83mW | 4.5µW     |

| dissipation                                      |                |        |           |

Table 2: Performance of the designed LPHG op-amp

# **IV. CONCLUSION**

The low power high gain op-amp has a mid-band gain of 106.733dB with a bandwidth of 1MHz while consuming  $4.5\mu$ W of power. This type of op-amp can be used in biomedical application because the bio-medical signal strength is low. In order to get the accurate results, an amplifier with high gain and stability is required. The presented op-amp has this capability.

# **V. REFERENCES**

- Ashish Singh, Ashwani K.Chandel, Rajeevan Chandel, Sanjay Singh Rajput, "Design of Low-Power High-Gain Operational Amplifier for Bio-Medical Applications", IEEE Computer Society Annual Symposium on VLSI, 2016.

- [2] Chaitanya, V. Jagan Naveen and B. M. S. Sreenivasa Rao, "Low Power High Gain Amplifier for Low Voltage Wearable Biomedical Applications", Indian Journal of Science and Technology, Vol 9(S1), December 2016.

- [3] R. G. H. Eschauzier, R. Hogervorst, and J. H. Huijsing, "A Programmable 1.5 V CMOS class-AB operational amplifier with hybrid nested miller compensation for 120 dB gain and 6 MHz UGF,"

- [4] IEEE Journal Solid-State Circuits, vol. 29, Dec. 1994.P. K. Ajmer, A. Srivastava, C. Zhang, "A 0.8V CMOS Amplifier Design", J. Analog Integrated Circuits and Signal Processing, vol. 47,pp. 315-321, 2006.

- [5] Kehul A. Shah, Purvi D. Patel, "Design of Low Power Two Stage CMOS Operational Amplifier", International Journal of Science and Research, Vol 2, March 2013.

- [6] R.S.Meena, Shruti Pancholi, "A Low Noise Two Stage Operational Amplifier on 45nm CMOS Process", International Research Journal of Engineering and Technology, Vol 3,February 2016.

Dr.S.Syed Ameer Abbas et al. International Journal of Recent Research Aspects ISSN: 2349-7688, Vol. 4, Issue 4, Dec 2017, pp. 312-315

- [7] C. H. Tsai, Z. H. Hsieh, and W. C. Fang, "A low-power lownoise CMOS analog front-end IC for portable brain-heart monitoring applications," Life Science Systems and Applications Workshop, pp. 43–46, 2011.

- [8] H. R. Dehsorkh, N. Ravanshad, R. Lotfi, K. Mafinezhad, and A.M.Sodagar, "Analysis and design of tunable amplifiers for implantable neural recording applications," IEEE Journal on Emerging and Selected Topics in Circuits and Systems, vol. 1, pp. 637-647, 2011.