# Review Report on VHDL (VHSIC Hardware description language)

Amit Grewal

School of Engineering & Technology, Ansal University, Gurugram, India

grewalamit1998@gmail.com

*Abstract*— This paper represents the review of VHDL which is a hardware description language that can be used to model a digital system at many level of abstraction. It is contemporary as it incorporates the popular and widely used IEEE. STD\_LOGIC\_1164 package. This language not only defines the syntax but also defines very clear simulation semantic for each language construct. The look is described by abstract interpretation of a static analysis for the popular hardware language VHDL. From a VHDL description, the analysis computes a superset of the state accessible throughout any simulation run. This information is beneficial within the validation of safety properties of hardware elements. The development of the analysis relies on the formal definition of linguistics for VHDL. Soundness with relevance this linguistics is shown. Varied techniques permit a compromise between the specified accuracy and therefore the value of the ultimate algorithmic rule.

*Keywords*— entity, port, in(input), out(output), end, architecture body, configuration declaration, package declaration, package body, signal, int(integer), statement (if, case null, exit, loop, next, assertion, report, wait), Hardware description language, VHSIC (Very high speed integrated circuit).

L

#### INTRODUCTION

VHDL is an acronym for VHSIC (very high speed integrated circuit). It is a hardware description language that can be used to model a digital system at many levels of abstraction, ranging from the algorithmic level to the gate level [1-2]. It is powerfully typewritten language and is usually windy to jot down. It inherits several of its options, particularly the sequent language half from the ADA artificial language. The entire language, however, has comfortable power to capture the outline of the foremost advanced chips to a whole electronic system.

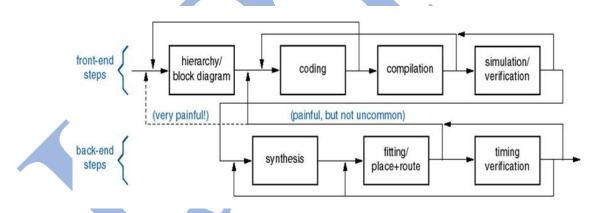

Fig. 1: Block Diagram of VHDL

VHDL may be a word form for terribly high speed computer circuit (VHSIC) Hardware Description Language that is an artificial language that describes a logic circuit by perform, information flow behavior and/or structure [3]. This hardware description is employed to tack a programmable logic device (PLD), like a field programmable gate array (FPGA), with a custom logic style [4-5]. The overall format of a VHDL program is constructed round the thought of BLOCKS that area unit the essential building units of a VHDL style. Among these style blocks a logic circuit of perform may be simply represented.

A VHDL style begins with associate degree ENTITY block that describes the interface for the planning. The interface defines the input and output llogic signals of the circuit being designed. The design block describes the interior operation of the planning. Among these blocks area unit various different useful blocks accustomed build the planning parts of the logic circuit being created.

When the planning is made, it may be simulated and synthesized to envision its logic operation. SIMULATION may be a clean bones style of take a look at to examine if the essential logic works in keeping with style and thought. SYNTHESIS permits temporal order factors and different influences of actual field programmable gate array (FPGA) devices to impact the simulation thereby doing a lot of thorough style of check before the planning is committed to the FPGA or similar device [6-10].

# Amit Grewal al. International Journal of Recent Research Aspects ISSN: 2349-7688, Vol. 5, Issue 1, March 2018, pp. 85-89

#### II. HISTORY AND BACKGROUND

First generated in 1981 under the VHSIC program. During this program, variety of U.S. corporations were concerned in coming up with VHSIC chips for the department of Defense (DOD). At that point, most of the businesses were mistreatment completely different hardware description language to explain and develop their integrated circuits Thus, a need for a standardized hardware description language for the design, documentation and verification of digital system was generated [20-21].

A team of three companies IBM, TAXAS INSTRUMENTS and INTERMETRICES were first awarded the contract by the DOD to develop a version of language in 1983 [22-25]. Version 7.2 of VHDL was developed and discharged to the general public in 1985. When the discharge of version seven.2 there was associate degree increasing have to be compelled to create the language associate degree industry-wide customary consequently, the language was transferred to the IEEE for standardization in 1986. when a considerable improvement to the language created by a team of trade, university and Defense Department representatives the language was standardized by the IEE in December 1987; this version of the language is understood because the IEE Std. 1076 -1987 [26].

Consequently, the language was upgraded with new features, the syntax of many construct was made more uniform and many ambiguities present in the 1987 version of the language were resolved. This new version of language is known as the IEEE std. 1076-1993. The summary of the major change made to the 1987 version of the language [27-28].

The department of defense, since Gregorian calendar month 1988, need all its digital application specific microcircuit (ASIC) provider to deliver VHDL description of the ASICs and their subcomponent at each the behavioral and structural level. This set of presidency needs is delineated in military commonplace 454. Since 1987, there has also been a great need for a standard package to aid in model interoperability. The outcomes of this committee was the development of at 9-values logic package. This package called STD\_LOGIC-1164 was then balloted and approved to become an IEEE standard, labeled IEEE std. 1164-1993 [29].

# III. APPLICATIONS

VHDL is employed primarily for the event of Application Specific Integrated Circuits (ASICs). Tools for the automated transformation of VHDL code into a gate-level internet list were developed already at Associate in nursing early purpose of your time. This transformation is termed synthesis Associate in nursing is an integral a part of current style flows. For the employment with Field Programmable Gate Arrays (FPGAs) many issues exist.

Within the beginning, mathematician equations are derived from the VHDL description, no matter, whether or not Associate in Nursing ASIC or a FPGA is that the target technology. But now, this mathematician code must be partitioned off into the configurable logic blocks (CLB) of the FPGA. This is often harder than the mapping onto Associate in Nursing ASIC library. Another massive drawback is that the routing of the CLBs because the out their resources for interconnections are the bottleneck of current FPGAs. Whereas synthesis tools cope practically with advanced styles, they get sometimes solely suboptimal results. Therefore, VHDL is hardly used for the planning of low complexness Programmable Logic Devices (PLDs).

VHDL are often applied to model system behavior severally from the target technology. This is often either helpful to produce customary solutions, e.g. for small controllers, error correction (de-)coders etc. or activity models of microprocessors and RAM devices are accustomed simulate a replacement device in its target setting. Associate in nursing current field of analysis is that the hardware/software co-design [11-12]. The foremost fascinating question is that half of the system ought to be enforced in software package and that part in hardware. The decisive constraints are the prices and also the ensuing performance.

#### IV. APPLICATION AREAS OF EACH LANGUAGE

ELLA is intended as a general-purpose hardware description language, and has the necessary infrastructure to support this. The language takes a structural view of hardware where designs are built up from components which are declared as functions or macros. VHDL is, like ELLA, meant to be used as a general-purpose language. Each is intended to support design from initial specification to implementation [13-17]. Silage is intended for high-level descriptions of DSP circuits in areas such as image processing or cryptography. Silage is not meant for low-level description of circuits; such descriptions of Silage programs are intended to be synthesized automatically.

# V. ADVANTAGE

# Amit Grewal al. International Journal of Recent Research Aspects ISSN: 2349-7688, Vol. 5, Issue 1, March 2018, pp. 85-89

The key advantage of VHDL, once used for systems style, is that it permits the behavior of the desired system to be represented (modeled) and verified (simulated) before synthesis tools translate the look into real hardware (gates and wires). Another profit is that VHDL permits the outline of a simultaneous system. VHDL may be a dataflow language, in contrast to procedural computing languages like BASIC, C, and assembly code, that all run consecutive, one instruction at a time.

A VHDL project is useful. Being created once, a calculation block is utilized in several alternative comes. However, several formational and purposeful block parameters is tuned (capacity parameters, memory size, part base, block composition and interconnection structure) [18-19]. A VHDL project is transportable. Being created for one part base, a computer project is ported on another part base, for instance VLSI with varied technologies.

A big advantage of VHDL compared to original Verilog is that VHDL incorporates a full sort system. Designers will use the kind system to write down way more structured code (especially by declaring record types).

## VI. CAPABILITIES

The following are the major capabilities that the language provides along with the features that differentiate it from other hardware description language [30].

- The language can be used as an exchange medium between chip vendors and CAD tool users.

- The language can also be used as a communication medium between CAD and CAE tools.

- The language supports hierarchy; that is a digital system can be modeled as asset of interconnected component; each component, in turn, can be modeled as a set of interconnected subcomponent.

- The language supports flexible design methodologies: top-down, bottom- up, or mixed.

- The language isn't technology-specific, however in capable of supporting technology-specific options. It can even support varied hardware technology.

- It supports both synchronous and asynchronous timing models.

- Various digital modeling techniques, such as finite-state machine description, algorithmic description, and Boolean equation, can be modeled using the language.

- The language is publically offered, human-readable, machine-readable, and specially it's not proprietary.

- It is associate IEEE and ANSI standard; thus, models represented exploitation this language moveable.

- The language supports three basic different description styles: structural, dataflow, and behavioral.

- It supports a good vary of abstraction level starting from abstract behavioral description to terribly precise gate-level description. It doesn't, however, support modeling at or below the electronic transistor level. It enables a style to be captured at a mixed level employing a single coherent language.

- Arbitrarily giant styles are sculptured victimisation the language, and there are not any limitations obligatory by the language on the dimensions of a style.

- The language has elements that make large-scale design modeling easier; for example, components, functions, procedures and package.

- Test benches may be written exploitation an equivalent language to check different VHDL models.

- Nominal propagation delays, min-max delays, setup and hold timing, timing constraints and spike detection can all be described very naturally in this language.

- The use of generics and attributes within the models facilitate back-annotation of static info like temporal order or placement info.

- Generics and attributes are also useful in describing parameterized designs.

- A model can not only describe the functionality of a design, but can also contain information about the design itself in terms of user defined attributes, such as total area and speed.

- A common language can be used to describe library component from different vendors.

- Models written in this language can be verified by simulation since precise simulation semantics are defined for each language construct.

- Behavioral models that adapt to a precise synthesis description vogue area unit capable of being synthesized to gate level description.

- The capability of defining new data types provides the power to describe and simulate a new design technique at a very high level of abstraction without any concern about the implementation details.

### VII. COMPARASION OF VHDL

The three languages ELLA, Silage and VHDL different along several dimensions, including intended applications, underlying behavioral model and generality. This makes it hard to compare them. Furthermore, the work on embedding each language has been done by different people having different stylistic tastes in writing formal

© 2018 IJRAA All Rights Reserved

# Amit Grewal al. International Journal of Recent Research Aspects ISSN: 2349-7688, Vol. 5, Issue 1, March 2018, pp. 85-89

specification, and has been driven by different project aims [31]. This section compares the three hardware description languages, while Section 5 gives an overview of the projects.

#### VIII. COMPARASION WITH 'C'

It is normally said that once you learn one programming language it is pretty easy to learn the other programming languages. This is as a result of the ideas square measure nearly same in most of the programming languages with some solely syntax variations. However, if you raise a hardware engineer, he might have a very totally different opinion. If you don't stop thinking from a C programmer's perspective, then life as VHDL computer user can drive you kooky. As a result of each the languages have several variations between them each square measure totally different from the fundamental level itself, although they appear to own several similarities [32-35].

Therefore, let Pine Tree State compile a number of the fundamental variations between C programming and VHDL programming.

- C is a middle level language. I mean it's a mix of a high level language and an assembly language. VHDL is a hardware description language (HDL). It is used for implementing the hardware circuit.

- C can only handle sequential instructions. VHDL allows both sequential and concurrent executions.

- A C program can be successfully written with pure logical or algorithmic thinking. But a successful VHDL programmer needs thorough working knowledge of the hardware circuits. He should be able to predict how a given code will be implemented in hardware.

- Normally we don't care about resource usage in C. This is because a C program is usually running on a computer which uses a powerful processor with high speed. We also don't care about the memory usage. But once it involves VHDL a rather difficult code will cause you to out to your knees. The memory and alternative logic components area unit restricted during a FPGA (where you usually place the VHDL code in). This can be why it's terribly tough to implement image process algorithms in VHDL than in C.

# IX. FUTURE SCOPE OF VHDL

VHDL is suited to the specification, style and outline of digital electronic hardware. System level VHDL isn't ideally suited to abstract system-level simulation, before the hardware-software split. Simulation at this level is sometimes random, and worries with modelling performance, throughput, queueing and applied math distributions. VHDL has been utilized in this space with some success, however is best suited to useful and not random simulation.

#### A. Digital Applications

VHDL is appropriate to be used these days within the digital hardware style method, from specification through high-level useful simulation, manual style and logic synthesis right down to gate-level simulation. VHDL tools sometimes give associate integrated style setting during this space.

VHDL is not suited to specialized implementation-level vogue verification tools like analog simulation, switch level simulation and worst case temporal property simulation. VHDL area unit usually accustomed simulate gate level unfold loading effects providing secret writing styles area unit adhered to and delay calculation tools area unit available. The standardization effort named important (VHDL Initiative towards ASIC Libraries) is active during this space, and is currently bearing fruit in this simulation vendors have integral important support. A lot of significantly, several ASIC vendors have VITAL-compliant libraries, although not all are permitting VITAL-based sign-off - not however anyway.

# B. Analogue Applications

In 1999, the IEEE approved normal 1076.1, that's informally referred to as VHDL-AMS. It's a real super-set of VHDL, and includes analog and mixed-signal extensions. Design method. This diagram below shows an awfully simplified read of the electronic system style method incorporating VHDL. The central portion of the diagram shows the components of the look method that are most wedged by VHDL.

The only company that I am aware still uses VHDL for designs in India is IBM and may be select few other companies that does projects for any European companies. Otherwise more than 90% companies use System Verilog that does have more scope.

#### X. CONCLUSION

The purpose of this paper was to study about VHDL as it is strongly typed language and is often verbose to write. Simple systems like this one are easily created & programmed and most errors are easily corrected. More complex systems are harder to work with. This platform is nice for beginners; it offers new learners the simplest way to ascertain the fundamentals of digital logic at work whereas conjointly seeing primitive style techniques.

# Amit Grewal al. International Journal of Recent Research Aspects ISSN: 2349-7688, Vol. 5, Issue 1, March 2018, pp. 85-89

#### ACKNOWLEDGMENT

The author gratefully acknowledges the authorities of School of Engineering and Technology, Ansal University, Gurgaon, India, for their constant encouragement and provision of facilities for this research work.

#### REFERENCES

- [1] Armstrong J.R, chip level modeling with VHDL, Englewood cliffs, NJ: prentice hall, 1988.

- [2] Armstrong, J.R.et al., the VHDL validation suite, proc. 27th design automation conference, June 1990, pp. 2-7.

- [3] Ashenden, P.J., The designer guide to VHDL, Morgan Kaufman, 1944.

- [4] Ashenden, P.J., the VHDL Cookbook, university of Adelaide, Australia, 1990.

- [5] Baker, L., VHDL programming with advanced topics, john Wiley and sons, Inc., 1993.

- [6] Barton, D., a first course in VHDL, VLSI systems design, January 1988.

- [7] Berge, J-M.et al., VHDL designer's reference, Kluwer academic, 1992.

- [8] Berge, J.-M.et al., VHDL '92, Kluwer academic, 1993.

- [9] Bhasker, J., A guide to VHDL syntax, Englewood cliffs, NJ: Prentice hall, 1994.

- [10] Bhasker, J., A VHDL synthesis primer, Allentown, PA: star galaxy publishing, 1995.

- [11] Bhasker, J., VHDL: features and applications, NJ: IEEE, order no. HL5712, 1996.

- [12] Bhasker, J., process- graph analyzer: a front-end tool for VHDL behavioral synthesis, software practice and experience, vol. 18, no. 5, may 1988.

- [13] Bhasker, J., an algorithm for microcode compaction of VHDL behavioral descriptions proc. 20th microprogramming workshop, December 1987.

- [14] Coelho, D., VHDL handbook, Boston: Kluwer academic, 1988.

- [15] Coelho, D., VHDL: a call for standard, proc. 25th design automation conference, June 1998.

- [16] Farrow, R., and A. Stanculescu, A VHDL compiler based on attribute Grammar methodology, SIGPLAN 1989.

- [17] Gilman, A.S., logic modeling in WAVES, IEEE design and test of computers, June 1990, pp. 49-55.

- [18] Hands, J.P., what is VHDL? Computers-aided design, vol. 22, no. 4, may 1990.

- [19] Harr, R., and A. Stanculescu (eds.), application of VHDL to circuit design, Boston: Kluwer academic, 1991.

- [20] Hines, J., where VHDL fits within the CAD environment, proc. 24<sup>th</sup> design automation conference, 1987.

[21] IEEE standard VHDL language reference manual, std. 1076-1987, IEEE, NY, 1988.

- [22] IEEE standard VHDL language reference manual, std. 1076-1993, IEEE, NY, 1993.

- [23] IEEE standard 1076 VHDL tutorial, CLSI, Maryland, march 1989.

- [24] IEEE standard interpretations: IEEE std. 1076-187, IEEE Standard VHDL language reference manual, IEEE, 1992.

- [25] IEEE standard multi value logic system for VHDL model interoperability (std\_logic\_1164), std. 1164\_1993, IEEE, 1993.

- [26] Kim, K., and J. Trout, automatic insertion of BIST hardware using VHDL, proc. 25th design automation conference, 1988.

- [27] Leung, ASIC system design with VHDL, Boston: Kluwer academic, 1989.

- [28] Lipsett, R.et. Al., VHDL: hardware description and design, Boston: Kluwer academic. 1989.

- [29] Moughzail, M.et. Al., experience with the VHDL environment, proc. 25th design automation conference, 1988.

- [30] Perry, D., VHDL, New York: McGraw hill, 1991.

- [31] Military standard 454, U.S. government printing Office, 1988.

- [32] Navabi, Z., VHDL analysis and modeling of digital system, McGraw hill, 1993.

- [33] Saunders, L., the IBM VHDL design system, proc. 24th design automation conference, 1987.

- [34] Schoen, J. M., performance and fault modeling with VHDL, Englewood cliffs, NJ: prentice hall, 1992.

- [35] Ward, P.C., and J. Armstrong, behavioral fault simulation in VHDL, proc. 27th design automation conference, June 1990, pp. 587-593.